Tou de SoC (Sistèm sou Chip) ak SiP (Sistèm nan Pake) se etap enpòtan nan devlopman sikui entegre modèn yo, ki pèmèt miniaturizasyon, efikasite ak entegrasyon sistèm elektwonik yo.

1. Definisyon ak Konsèp Debaz SoC ak SiP

SoC (Sistèm sou Chip) - Entegre tout sistèm nan nan yon sèl chip

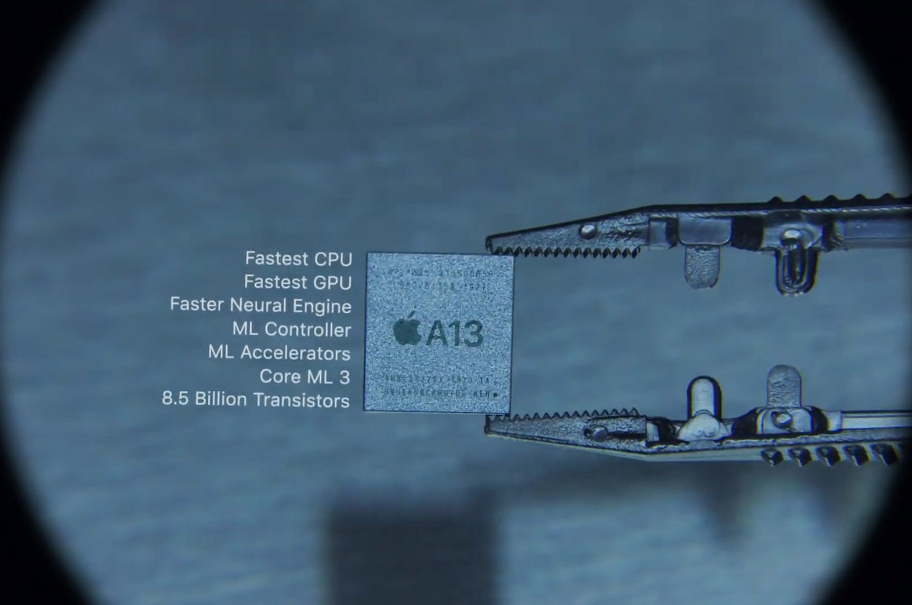

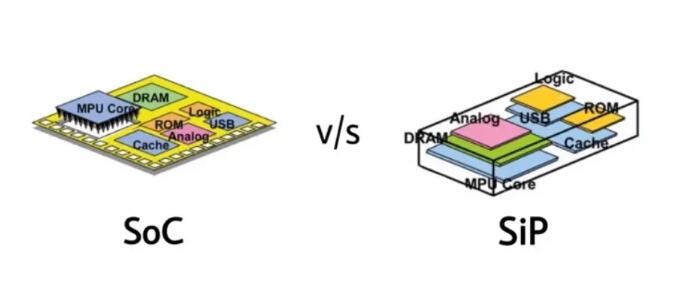

Yon SoC tankou yon grat syèl, kote tout modil fonksyonèl yo fèt epi entegre nan menm chip fizik la. Lide prensipal SoC a se entegre tout konpozan prensipal yon sistèm elektwonik, tankou processeur a (CPU), memwa, modil kominikasyon, sikui analòg, koòdone detèktè, ak plizyè lòt modil fonksyonèl, sou yon sèl chip. Avantaj SoC yo chita nan wo nivo entegrasyon li ak ti gwosè li, sa ki bay benefis enpòtan nan pèfòmans, konsomasyon enèji, ak dimansyon, sa ki fè li patikilyèman apwopriye pou pwodwi ki gen gwo pèfòmans e ki sansib a enèji. Processeur ki nan smartphones Apple yo se egzanp chip SoC.

Pou nou montre sa, yon SoC se tankou yon "super bilding" nan yon vil, kote tout fonksyon yo fèt anndan, epi plizyè modil fonksyonèl yo tankou diferan etaj: gen kèk ki se zòn biwo (processeur), gen kèk ki se zòn amizman (memwa), epi gen kèk ki se rezo kominikasyon (interfaces kominikasyon), tout konsantre nan menm bilding lan (chip). Sa pèmèt tout sistèm nan fonksyone sou yon sèl chip silikon, pou rive nan pi gwo efikasite ak pèfòmans.

SiP (Sistèm nan Pakè) - Konbine diferan chip ansanm

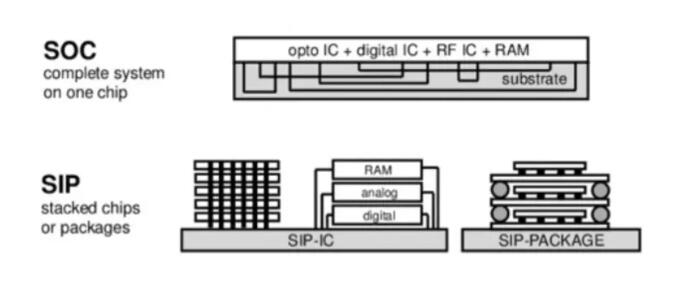

Apwòch teknoloji SiP a diferan. Li plis tankou anbalaj plizyè chip ak diferan fonksyon nan menm anbalaj fizik la. Li konsantre sou konbine plizyè chip fonksyonèl atravè teknoloji anbalaj olye ke entegre yo nan yon sèl chip tankou SoC. SiP pèmèt plizyè chip (processeur, memwa, chip RF, elatriye) yo dwe pake kòt a kòt oswa anpile nan menm modil la, fòme yon solisyon nivo sistèm.

Konsèp SiP a ka konpare ak rasanble yon bwat zouti. Bwat zouti a ka gen diferan zouti, tankou tournevis, mato, ak dril. Malgre ke yo se zouti endepandan, yo tout ini nan yon sèl bwat pou itilizasyon pratik. Avantaj apwòch sa a se ke chak zouti ka devlope epi pwodui separeman, epi yo ka "rasanble" nan yon pake sistèm jan sa nesesè, sa ki bay fleksibilite ak vitès.

2. Karakteristik teknik ak diferans ant SoC ak SiP

Diferans Metòd Entegrasyon:

SoC: Diferan modil fonksyonèl (tankou CPU, memwa, I/O, elatriye) yo fèt dirèkteman sou menm chip silikon an. Tout modil yo pataje menm pwosesis fondamantal la ak lojik konsepsyon an, pou fòme yon sistèm entegre.

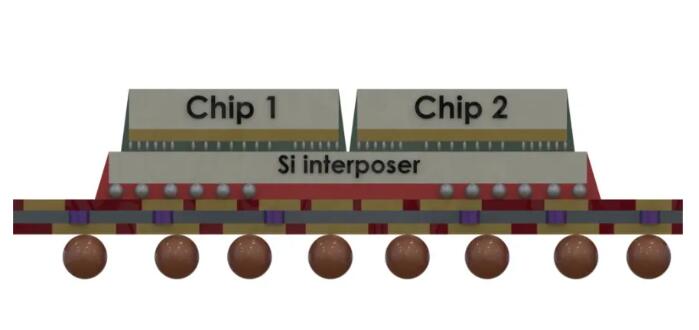

SiP: Yo ka fabrike diferan chip fonksyonèl lè l sèvi avèk diferan pwosesis epi answit konbine yo nan yon sèl modil anbalaj lè l sèvi avèk teknoloji anbalaj 3D pou fòme yon sistèm fizik.

Konpleksite ak Fleksibilite nan Konsepsyon:

SoC: Piske tout modil yo entegre sou yon sèl chip, konpleksite konsepsyon an trè wo, sitou pou konsepsyon kolaboratif diferan modil tankou dijital, analòg, RF, ak memwa. Sa mande pou enjenyè yo gen kapasite konsepsyon kwa-domèn pwofon. Anplis, si gen yon pwoblèm konsepsyon ak nenpòt modil nan SoC a, tout chip la ka bezwen reamenaje, sa ki poze risk enpòtan.

SiP: Okontrè, SiP ofri plis fleksibilite nan konsepsyon. Yo ka konsepsyone epi verifye diferan modil fonksyonèl separeman anvan yo entegre yo nan yon sistèm. Si yon pwoblèm rive ak yon modil, se sèlman modil sa a ki bezwen ranplase, sa ki pa afekte lòt pati yo. Sa pèmèt tou vitès devlopman ki pi rapid epi mwens risk konpare ak SoC.

Konpatibilite Pwosesis ak Difikilte:

SoC: Entegrasyon diferan fonksyon tankou dijital, analòg, ak RF sou yon sèl chip fè fas ak gwo defi nan konpatibilite pwosesis. Diferan modil fonksyonèl mande diferan pwosesis fabrikasyon; pa egzanp, sikui dijital bezwen pwosesis gwo vitès, ki pa konsome anpil enèji, alòske sikui analòg yo ka mande yon kontwòl vòltaj ki pi presi. Reyalize konpatibilite ant diferan pwosesis sa yo sou menm chip la trè difisil.

SiP: Atravè teknoloji anbalaj, SiP ka entegre chip ki fabrike lè l sèvi avèk diferan pwosesis, pou rezoud pwoblèm konpatibilite pwosesis teknoloji SoC a ap fè fas. SiP pèmèt plizyè chip eterogèn travay ansanm nan menm anbalaj la, men egzijans presizyon pou teknoloji anbalaj yo wo anpil.

Sik ak Pri R&D:

SoC: Piske SoC mande pou konsepsyon ak verifikasyon tout modil yo depi nan kòmansman, sik konsepsyon an pi long. Chak modil dwe sibi yon konsepsyon, verifikasyon ak tès ki rigoureux, epi pwosesis devlopman an jeneral ka pran plizyè ane, sa ki lakòz gwo depans. Sepandan, yon fwa li antre nan pwodiksyon an mas, pri inite a pi ba akòz gwo entegrasyon an.

SiP: Sik R&D a pi kout pou SiP. Paske SiP itilize dirèkteman chip fonksyonèl ki deja egziste epi verifye pou anbalaj, li diminye tan ki nesesè pou reamenaje modil la. Sa pèmèt lansman pwodwi pi rapid epi li diminye depans R&D yo anpil.

Pèfòmans ak gwosè sistèm:

SoC: Piske tout modil yo sou menm chip la, reta kominikasyon, pèt enèji, ak entèferans siyal yo minimize, sa ki bay SoC yon avantaj san parèy nan pèfòmans ak konsomasyon enèji. Gwosè li minim, sa ki fè li patikilyèman apwopriye pou aplikasyon ki gen gwo pèfòmans ak bezwen enèji, tankou smartphones ak chip pwosesis imaj.

SiP: Malgre nivo entegrasyon SiP a pa osi wo ke SoC a, li ka toujou pake diferan chip ansanm yon fason konpak lè l sèvi avèk teknoloji anbalaj milti-kouch, sa ki lakòz yon gwosè ki pi piti konpare ak solisyon milti-chip tradisyonèl yo. Anplis, piske modil yo pake fizikman olye ke entegre sou menm chip silikon an, alòske pèfòmans lan ka pa koresponn ak SoC a, li ka toujou satisfè bezwen pifò aplikasyon yo.

3. Senaryo Aplikasyon pou SoC ak SiP

Senaryo Aplikasyon pou SoC:

SoC tipikman apwopriye pou domèn ki gen gwo egzijans an tèm de gwosè, konsomasyon enèji, ak pèfòmans. Pa egzanp:

Telefòn entelijan: Procesè ki nan telefòn entelijan yo (tankou chip seri A Apple yo oubyen Snapdragon Qualcomm nan) anjeneral se SoC trè entegre ki enkòpore CPU, GPU, inite pwosesis IA, modil kominikasyon, elatriye, ki mande tou de pèfòmans pwisan ak konsomasyon enèji ki ba.

Tretman Imaj: Nan kamera dijital ak dron, inite tretman imaj yo souvan mande pou gwo kapasite tretman paralèl ak latans ki ba, sa SoC ka reyalize efektivman.

Sistèm Entegre Pèfòmans Segondè: SoC patikilyèman apwopriye pou ti aparèy ki gen egzijans efikasite enèji strik, tankou aparèy IoT ak aparèy pòtab.

Senaryo Aplikasyon pou SiP:

SiP gen yon seri senaryo aplikasyon ki pi laj, apwopriye pou domèn ki mande devlopman rapid ak entegrasyon milti-fonksyonèl, tankou:

Ekipman Kominikasyon: Pou estasyon baz, routeurs, elatriye, SiP ka entegre plizyè processeur siyal RF ak dijital, sa ki akselere sik devlopman pwodwi a.

Elektwonik pou konsomatè: Pou pwodwi tankou mont entelijan ak kas ekoutè Bluetooth, ki gen sik amelyorasyon rapid, teknoloji SiP pèmèt lansman pi rapid nan nouvo pwodwi karakteristik.

Elektwonik otomobil: Modil kontwòl ak sistèm rada nan sistèm otomobil yo ka itilize teknoloji SiP pou entegre rapidman diferan modil fonksyonèl.

4. Tandans Devlopman SoC ak SiP nan lavni

Tandans nan Devlopman SoC:

SoC a ap kontinye evolye nan direksyon pou yon pi gwo entegrasyon ak entegrasyon etewojèn, ki potansyèlman enplike plis entegrasyon processeur IA, modil kominikasyon 5G, ak lòt fonksyon, pou kondwi plis evolisyon aparèy entelijan yo.

Tandans nan Devlopman SiP:

SiP pral de pli zan pli konte sou teknoloji anbalaj avanse, tankou avansman anbalaj 2.5D ak 3D, pou byen pake chip ak diferan pwosesis ak fonksyon ansanm pou satisfè demand mache a k ap chanje rapidman.

5. Konklizyon

SoC plis tankou bati yon gwo grat syèl miltifonksyonèl, ki konsantre tout modil fonksyonèl yo nan yon sèl konsepsyon, apwopriye pou aplikasyon ki gen egzijans trè wo an tèm de pèfòmans, gwosè ak konsomasyon enèji. SiP, bò kote pa l, se tankou "anbale" diferan chip fonksyonèl nan yon sistèm, ki konsantre plis sou fleksibilite ak devlopman rapid, patikilyèman apwopriye pou elektwonik konsomatè ki mande mizajou rapid. Tou de gen fòs yo: SoC mete aksan sou pèfòmans optimal sistèm ak optimize gwosè, pandan ke SiP mete aksan sou fleksibilite sistèm ak optimize sik devlopman an.

Dat piblikasyon: 28 oktòb 2024